SDR receiver compatible with HPSDR

Introduction

This version of the SDR receiver emulates two Hermes modules with eight receivers. It may be useful for projects that require sixteen receivers compatible with the programs that support the HPSDR/Metis communication protocol.

The HPSDR/Metis communication protocol is described in the following documents:

Hardware

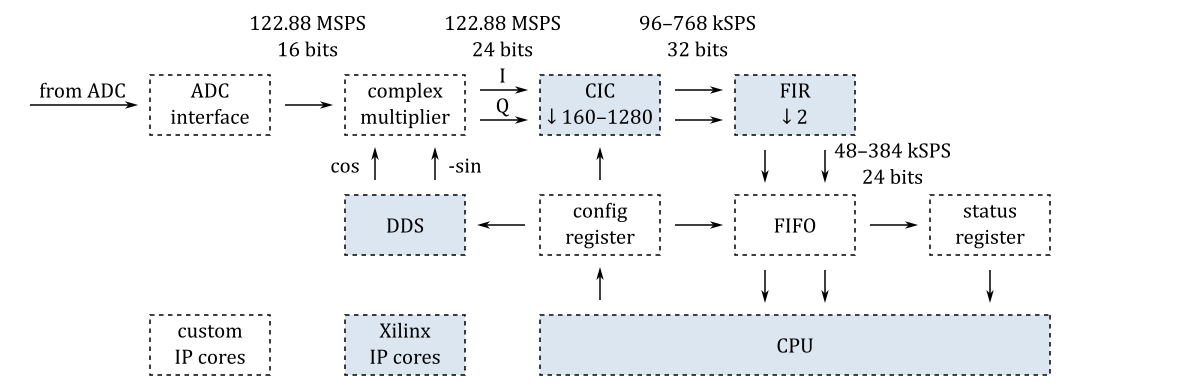

The FPGA configuration consists of sixteen identical digital down-converters (DDC). Their structure is shown in the following diagram:

The I/Q data rate is configurable and four settings are available: 48, 96, 192, 384 kSPS.

The tunable frequency range covers from 0 Hz to 61.44 MHz.

The projects/sdr_receiver_hpsdr_122_88 directory contains two Tcl files: block_design.tcl, rx.tcl. The code in these files instantiates, configures and interconnects all the needed IP cores.

The projects/sdr_receiver_hpsdr_122_88/filters directory contains the source code of the R scripts used to calculate the coefficients of the FIR filters.

The projects/sdr_receiver_hpsdr_122_88/server directory contains the source code of the UDP server (sdr-receiver-hpsdr.c) that receives control commands and transmits the I/Q data streams to the SDR programs.

Software

This SDR receiver should work with most of the programs that support the HPSDR/Metis communication protocol:

PowerSDR mRX PS that can be downloaded from this link

QUISK with the

hermes/quisk_conf.pyconfiguration fileghpsdr3-alex client-server distributed system

openHPSDR Android Application that is described in more details at this link

Java desktop application based on openHPSDR Android Application

Getting started

- Download SD card image zip file (more details about the SD card image can be found at this link).

- Copy the contents of the SD card image zip file to a micro SD card.

- Optionally, to start the application automatically at boot time, copy its

start.shfile fromapps/sdr_receiver_hpsdr_122_88to the topmost directory on the SD card. - Install the micro SD card in the STEMlab SDR board and connect the power.

- Install and run one of the HPSDR programs.

Running CW Skimmer Server and Reverse Beacon Network Aggregator

- Install CW Skimmer Server.

- Copy HermesIntf.dll to the CW Skimmer Server program directory (

C:\Program Files (x86)\Afreet\SkimSrv). - In the

SkimSrvdirectory, renameHermesIntf.dlltoHermestIntf_XXXX.dllwhereXXXXare the last four digits of the MAC address of the STEMlab SDR. - Make a copy of the

SkimSrvdirectory and rename the copy toSkimSrv2. - In the

SkimSrv2directory, renameSkimSrv.exetoSkimSrv2.exeand renameHermestIntf_XXXX.dlltoHermestIntf_FFXX.dll. - Install Reverse Beacon Network Aggregator.

- Start

SkimSrv.exeandSkimSrv2.exe, configure frequencies and your call sign. - Start Reverse Beacon Network Aggregator.

Building from source

The installation of the development machine is described at this link.

The structure of the source code and of the development chain is described at this link.

Setting up the Vitis and Vivado environment:

source /opt/Xilinx/2025.2/Vitis/settings64.shCloning the source code repository:

git clone https://github.com/pavel-demin/red-pitaya-notes

cd red-pitaya-notesBuilding sdr_receiver_hpsdr_122_88.bit:

make NAME=sdr_receiver_hpsdr_122_88 PART=xc7z020clg400-1 bitBuilding SD card image zip file:

source helpers/build-all.sh